Product Summary

The HYE18L256160BC-7.5 is a high-speed CMOS, dynamic random-access memory containing 268,435,456 bits. It is internally configured as a quad-bank DRAM. The HYE18L256160BC-7.5 achieves high speed data transfer rates by employing a chip architecture that prefetches multiple bits and then synchronizes the output data to the system clock. The HYE18L256160BC-7.5 is especially designed for mobile applications. It operates from a 1.8V power supply. Power consumption in self refresh mode is drastically reduced by an On-Chip Temperature Sensor (OCTS); it can further be reduced by using the programmable Partial Array Self Refresh (PASR).

Parametrics

HYE18L256160BC-7.5 absolute maximum ratings: (1)Power Supply Voltage VDD: -0.3 to 2.7 V; (2)Power Supply Voltage for Output Buffer VDDQ: -0.3 to 2.7 V; (3)Input Voltage VIN: -0.3 to VDDQ + 0.3 V; (4)Output Voltage VOUT: -0.3 to VDDQ + 0.3 V; (5)Operation Case Temperature Commercial TC: 0 to +70 ℃, Extended TC: -25 to +85 ℃; (6)Storage Temperature TSTG: -55 to +150 ℃; (7)Power Dissipation PD: 0.7 W; (8)Short Circuit Output Current IOUT: 50 mA.

Features

HYE18L256160BC-7.5 features: (1) 4 banks × 4 Mbit × 16 organisation; (2)Fully synchronous to positive clock edge; (3)Four internal banks for concurrent operation; (4)Programmable CAS latency: 2, 3; (5)Programmable burst length: 1, 2, 4, 8 or full page; (6)Programmable wrap sequence: sequential or interleaved; (7)Auto refresh and self refresh modes; (8)8192 refresh cycles / 64ms; (9)Auto precharge; (10)54-ball FBGA package (12.0 mm × 8.0 mm × 1.0 mm).

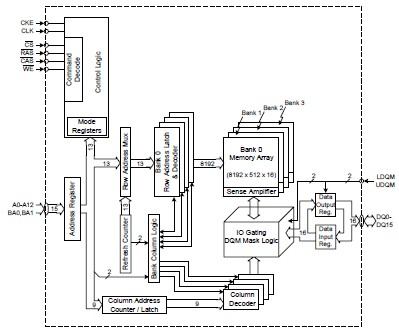

Diagrams

|

HYE18L512320BF-7.5 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYE18M512160BF-6 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYE18M512160BF-7.5 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYE18P16161AC-70 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYE18P16161AC-85 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYE18P16161AC-L70 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))