Product Summary

The D80C187-12 is a high-performance math coprocessor that extends the architecture of the 80C186 with floating-point, extended integer, and BCD data types. A computing system that includes the D80C187-12 fully conforms to the IEEE Floating-Point Standard. The 80C187 adds over seventy mnemonics to the instruction set of the 80C186, including support for arithmetic, logarithmic, exponential, and trigonometric mathematical operations. The D80C187-12 is implemented with 1.5 micron, high-speed CHMOS III technology and packaged in both a 40-pin CERDIP and a 44-pin PLCC package. The D80C187-12 is upward object-code compatible from the 8087 math coprocessor and will execute code written for the 80387DX and 80387SX math coprocessors.

Parametrics

D80C187-12 absolute maximum ratings: (1)Case Temperature Under Bias (TC): 0℃ to +85℃; (2)Storage Temperature: -65℃ to +150℃; (3)Voltage on Any Pin with Respect to Ground: -0.5V to VCC +0.5V; (4)Power Dissipation: 1.5W.

Features

D80C187-12 features: (1) High Performance 80-Bit Internal Architecture; (2) Implements ANSI/IEEE Standard 754- 1985 for Binary Floating-Point Arithmetic; (3) Upward Object-Code Compatible from 8087; (4) Fully Compatible with 387DX and 387SX Math Coprocessors. Implements all 387 Architectural Enhancements over 8087; (5) Directly Interfaces with 80C186 CPU; (6) 80C186/80C187 Provide a Software/ Binary Compatible Upgrade from 80186/82188/8087 Systems; (7) Built-In Exception Handling; (8) Available in 40-Pin CERDIP and 44-Pin PLCC Package.

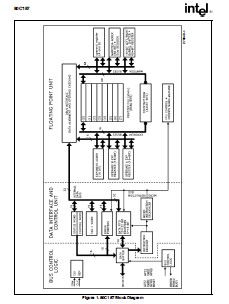

Diagrams

|

D80C31BH1SF88 |

Intel |

IC MPU 8-BIT 5V 16MHZ 40-CDIP |

Data Sheet |

Negotiable |

|

||||

|

D80C51FA1SF88 |

Intel |

IC MPU 8-BIT 5V 16MHZ 40-CDIP |

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))