Product Summary

The XC4010XL-1PQ208C is a high-performance, high-capacity Field Programmable Gate Array (FPGA) provides the benefits of custom CMOS VLSI, while avoiding the initial cost, long development cycle, and inherent risk of a conventional masked gate array. The result of thirteen years of the XC4010XL-1PQ208C design experience and feedback from thousands of customers, the XC4010XL-1PQ208C combines architectural versatility, on-chip Select-RAM memory with edge-triggered and dual-port modes, increased speed, abundant routing resources, and new, sophisticated software to achieve fully automated implementation of complex, high-density, high-performance designs.

Parametrics

XC4010XL-1PQ208C absolute maximum ratings: (1)CCLK (output) Delay TICCK: 40, 250 μs; (2)CCLK (output) Period, slow TCCLK: 640, 2000 ns; (3)CCLK (output) Period, fast TCCLK: 80, 250 ns; (4)CCLK (output) Delay TICCK: 40, 250 ms; (5)CCLK (output) Period, slow TCCLK: 540, 1600 ns; (6)CCLK (output) Period, fast TCCLK: 67, 200 ns.

Features

XC4010XL-1PQ208C features: (1) Highest Performance —3.3 V XC4000XL; (2) Highest Capacity —Over 180,000 Usable Gates; (3) 5 V tolerant I/Os on XC4000XL; (4) 0.35 μm SRAM process for XC4000XL; (5) Additional Routing Over XC4000E; (6) Buffered Interconnect for Maximum Speed Blocks; (7) Improved VersaRingTM I/O Interconnect for Better Fixed; (8)Pinout Flexibility; (9) 12 mA Sink Current Per XC4000X Output.

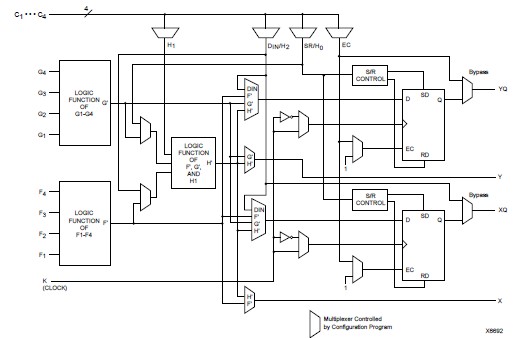

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

XC4010XL-1PQ208C |

|

IC FPGA C-TEMP 3.3V 1SPD 208PQFP |

Data Sheet |

Negotiable |

|

||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|

XC4000 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000E |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000H |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000X |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000XL |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))